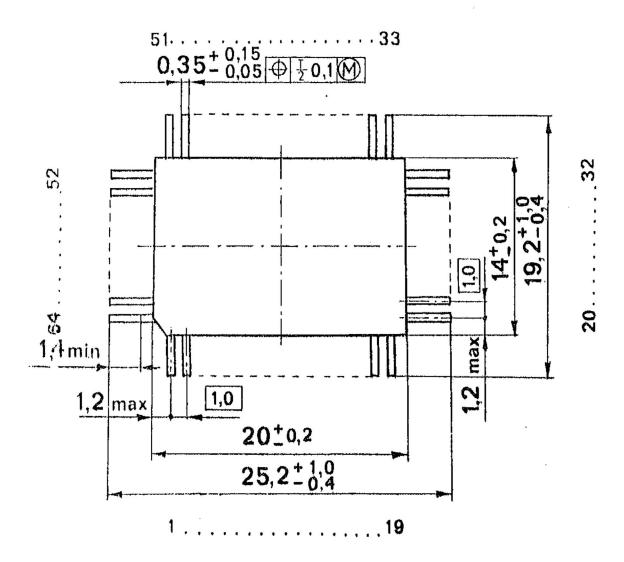

Anschlußbelegung

Bauform: PLCC-68, (Bild 32)

| Bezeichnung | der | Anschlüsse |

|-------------|-----|------------|

CLKI Eingang Eingangstakt

90

CLKO Ausgang Taktausgabe der Normalfrequenz

DAL

RESET Eingang RESET des Schaltkreises

BM 0 ... BM 3 Ausgänge Byte-Maske

DAL 00 ... DAL 31 Ein-/Ausgänge, Daten-/Adreßbus

Tristate gemultiplexer, 32 Bit breiter

Bus zur Adreß- u. Datenkommunikation

IRO 3 IRO 2 TEST

As Ausgang, Tristate Adress strobe

DS Ausgang, Tristate Data strobe

DBE Ausgang, Tristate Data buffer enable

WR Ausgang, Tristate Write

EPS Ausgang External processor strobe

CS 0, CS 1 Ausgänge, Tristate Bus cycle status

CS 2 Ein-/Ausgang, Tristate Bus cycle status

RDY Eingang Ready

Eingang Error ERR Eingang DMA request DMR Ausgang DMA grant DMG Halt-Interrupt-Anforderung Eingang HALT Timer-Interrupt-Anforderung INTTIM Eingang Power-Fail-Interrupt-Anforderung Eingang PWRFL IRQ 0 ... IRQ 3 Interrupt-Anforderung für Standard-IO-Interruppts Eingänge Testeingang für Bauelementehersteller Eingang TEST Betriebsspannung zur Versorgung der Pinlogik d. Daten-/Adreßbusses  $U_{CCX}$ Bezugspotential für U<sub>CCX</sub>  $U_{SSX}$ Betriebsspannung für UCCI CPU DAL 00 Schaltkreislogik 20 21 DAL 01 BM 0 Bezugspotential für  $U_{CCI}$ DAL 02 **BM 1**  $U_{SSI}$ 22 DAL 03 **BM 2** 23 DAL 04 **BM 3** Bulkspannung,  $U_{\mathrm{BB}}$ 29 DAL 05 WR 30 intern generiert DAL 06 DMG 31 67 DAL 07 EPS 37 66 DAL 08 DS 36 65 DBE **DAL 09** 64 38 DAL 10 AS 63 DAL 11 62 DAL 12 61 **DAL 13** 60 DAL 14 59 DAL 15 DAL 16 57 **DAL 17** 56 DAL 18 <u>55</u> **DAL 19** 54 **DAL 20** 53 **DAL 21** 50 DAL 22 49 DAL 23 48 DAL 24 47 DAL 25 46 DAL 26 45 DAL 27 44. **DAL 28** 43 **DAL 29** 42 **DAL 30** 41 DAL 31 28 ERR 27 RDY 26 35 CLKO DMR CLKI 24 RESET 19 HALT 18 INTTIM 16 34 CS 0 PWRFL 15 33 CS 1 IRQ 0 14 **IRQ 1** 12 IRQ 2 11 **IRQ 3** 32 CS 2 13 TEST Schaltzeichen

Der U 80701 FC ist ein in nSG-Technologie hergestellter 32 Bit Mikroprozessor. Er er möglicht den Aufbau von Rechnern hoher Leistungsfähigkeit. Er ist für Mehrnutzer und Echtzeitanwendungen geeignet.

Der Schaltkreis U 80701 FC ist ein Mikroprozessor mit voller 32 Bit Architektur, d.h. er besitzt einen externen und internen 32 Bit Daten-/Adreßbus. Der Einsatz dieses Mikroprozessors zusammen mit den anderen Bausteinen des 32 Bit Mikroprozessorsystems mit hoher Verarbeitungsgeschwindigkeit (Taktfrequenz 40 MHz) erlaubt den Aufbau von Rechnern mit lokal und global vernetztem Datenaustausch.

## Eigenschaften

- Volle 32 Bit Archikektur

- \* Realisierung der RVS-Archikektur

- \* externe und interne 32 Bit Datenbusse

- \* externe und interne 32 Bit Adressbusse,

!

- hohe Verarbeitungsgeschwindigkeit:

- \* Bei einer Taktfrequenz von 40 MHz wird eine Durchsatzrate von ca. 1 MIPS erreicht.

- \* Die ALU liest innerhalb von 200 ns zwei Operanden, führt eine ALU- oder SHIFT-Operation aus und legt das Ergebnis in ein Register ab,

- großer Adreß-Raum

- \* 16 MByte physikalischer Speicher

- \* 4 GByte virtueller Speicher,

- integrierte Speicherverwaltungseinheit (MMU) und zwei Adressumsetzpuffer virtuellphysische Adressumsetzung in 25 ns bei Vorhandensein eines gültigen Eintrags im Puffer, einen 512 Byte seitenorientierten Schutzmechanismus sowie eine Verwaltung der Zugriffsrechte (Protection),

- realisierung von 175 verschiedenen Maschinenbefehlen, alle Befehle sind orthogonal in ihrer Struktur und lassen für jeden der maximal 6 Operanden alle der 21 verschiedenen Adressenmodi zu,

- die Abarbeitung der Maschinenbefehle erfolgt mikroprogrammgesteuert, das Mikroprogramm ist in einem 62,4 kByte ROM auf dem Chip gespeichert, zur Beschleunigung der Befehlsabarbeitung ist ein acht Byte tiefer prefetch-stack integriert,

- 15 softwarenmäßig programmierbare Interruptebenen (software interrupt levels) und 7 Interrupteingänge (hardware interrupt inputs) werden unterstützt,

- Registersatz \* 16; 32 Bit breite allgemeine Register

- \* 20 Prozessor-bzw. interne Register,

- integrierter Bulkspannungsgenerator,

- Option für Co-Prozessor Anschluss (Floating Point Unit-FPU).